文章内容如有错误或排版问题,请提交反馈,非常感谢!

引脚分类概览

51单片机引脚可分为5大类:

| 类别 | 引脚数量 | 核心功能 |

| 电源引脚 | 2 | VCC(+5V)、GND(接地) |

| 时钟引脚 | 2 | XTAL1、XTAL2(外接晶振) |

| 复位引脚 | 1 | RST(高电平复位) |

| I/O口引脚 | 32 | P0、P1、P2、P3(每组8位共32引脚) |

| 控制引脚 | 3 | EA、ALE、PSEN(扩展模式用) |

核心引脚详解表

| 引脚名称 | 引脚号 | 功能 | 关键特性 |

| P0口 | 32-39 | 8位双向I/O口 | 开漏输出:需外接上拉电阻(常用4.7KΩ) 复用功能:作为外部存储器的低8位地址/数据总线 |

| P1口 | 1-8 | 8位准双向I/O口 | 纯I/O口:无复用功能,最常用 内置弱上拉电阻,可直接驱动LED |

| P2口 | 21-28 | 8位准双向I/O口 | 复用功能:访问外部存储器时,提供高8位地址 |

| P3口 | 10-17 | 8位准双向I/O口 + 第二功能 | 第二功能为核心:需优先用于通信/中断 (见下方第二功能表) |

| RST | 9 | 复位输入(高电平有效) | 持续高电平>2个机器周期触发复位 典型电路:10uF电容+10KΩ电阻复位电路 |

| XTAL1/2 | 18、19 | 外接晶振或外部时钟输入 | 晶振频率范围:4-48MHz 常用值:11.0592MHz(串口无误差) |

| EA | 31 | 程序存储器选择端 | 接VCC:优先使用片内Flash 接地:强制使用外部程序存储器 |

P3口的第二功能(必记!)

复用功能优先级高于普通I/O!

| P3引脚 | 第二功能符号 | 功能说明 |

| P3.0 | RXD | 串行数据接收(如:连接CH340下载器) |

| P3.1 | TXD | 串行数据发送(下载程序的关键引脚) |

| P3.2 | INT0 | 外部中断0(低电平/下降沿触发) |

| P3.3 | INT1 | 外部中断1 |

| P3.4 | T0 | 定时器/计数器0外部输入 |

| P3.5 | T1 | 定时器/计数器1外部输入 |

| P3.6 | WR | 外部数据存储器写使能(扩展RAM用) |

| P3.7 | RD | 外部数据存储器读使能 |

初学者核心实践要点

- 避开复用陷阱:

- P0口做I/O时必须外接上拉电阻(开发板通常已集成)。

- P3口优先服务于第二功能(串口、中断),勿随意接传感器。

- 最小系统引脚:

- 供电:VCC(40脚)+ GND(20脚)接5V电源。

- 复位:RST(9脚)+ 复位电路。

- 时钟:XTAL1(18脚)+ XTAL2(19脚)+ 11.0592MHz晶振 + 30pF电容×2。

- 下载:0(RXD)、P3.1(TXD)连接USB转TTL工具(如CH340)。

- 引脚驱动能力:

- 单个I/O最大输出电流约10mA(避免直接驱动大功率设备)。

- 驱动继电器/电机需用三极管或MOSFET隔离。

51单片机GPIO

GPIO基础概念

- 定位:单片机与外部设备交互的物理接口(共4组8位端口:P0/P1/P2/P3,32个I/O引脚)

- 核心功能:

- 输出:驱动LED、继电器、蜂鸣器等(控制高低电平)

- 输入:读取按键、传感器信号(检测电平状态)

- 关键特性:

- 双向I/O

- 部分引脚复用(如P3的第二功能)

- 驱动能力有限(需注意电流限制)

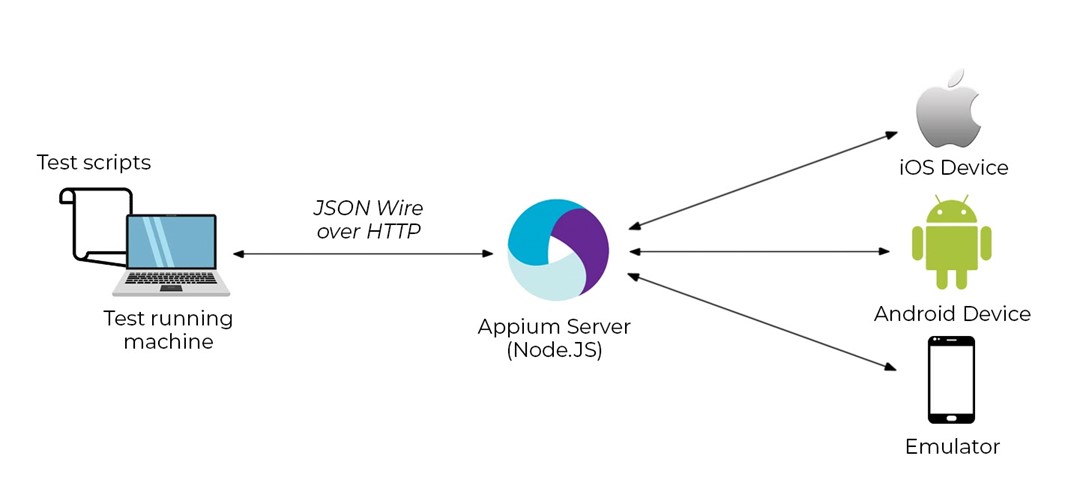

GPIO内部结构详解

所有端口的共性结构

+---------------------+

| 锁存器(D触发器) | ← 保存输出状态(写入Px)

+----------+----------+

|

+----------+----------+

| 输出驱动器 | ← 推挽/开漏结构

+----------+----------+

|

+----------+----------+

| 输入缓冲器 | ← 读取引脚/锁存器状态

+----------+----------+

|

Px.x引脚

- 锁存器:存储用户写入的值(如P1 = 0xFE;)

- 输出驱动器:将锁存器值转换为实际电平输出

- 输入缓冲器:允许读取引脚实时电平或锁存器状态

各端口差异对比

| 端口 | 内部上拉 | 引脚数 | 驱动能力 | 输出结构 | 复用功能 | 驱动电流 |

| P0 | ❌ 无 | 8 (P0.0-P0.7) | 8个TTL负载 | 开漏输出 | 地址/数据总线(低8位) | 高电平弱,低电平强 |

| P1 | ✅ 有(≈30kΩ) | 8 (P1.0-P1.7) | 4个TTL负载 | 准双向口(推挽) | 通用I/O | 高/低电平均中等 |

| P2 | ✅ 有(≈30kΩ) | 8 (P2.0-P2.7) | 4个TTL负载 | 准双向口(推挽) | 地址总线(高8位) | 高/低电平均中等 |

| P3 | ✅ 有(≈30kΩ) | 8 (P3.0-P3.7) | 4个TTL负载 | 准双向口(推挽) | 第二功能(串口/中断) | 高/低电平均中等 |

注:

- 准双向口:输出高电平时为弱上拉,低电平时为强下拉(P1/P2/P3)

- 开漏输出:仅能强下拉,高电平需外部上拉(P0)

各端口深度解析

P0端口

- 电路结构:

- 包含两个场效应管(FET):一个用于数据输出,另一个作为总线开关

- 无内部上拉电阻,需外接10kΩ上拉电阻才能输出高电平

- 工作模式:

- 普通I/O模式:需软件置1后通过外接上拉电阻输出高电平

- 地址/数据总线模式(当EA=0或访问外部存储器时自动启用):

- 分时输出低8位地址(A0-A7)和8位数据(D0-D7)

- 通过ALE信号锁存地址

- 典型应用:

- 扩展外部存储器(如6264 SRAM)

- 连接LCD1602的数据总线

// P0作为数据总线示例

#define DATA_BUS P0

void Write_Data(unsigned char dat) {

DATA_BUS = dat;

E = 1; // 使能LCD

_nop_();

E = 0;

}

P1端口

- 电路结构:

- 准双向口结构,内置20kΩ弱上拉电阻

- 输入前需先写1(释放端口)

- 特殊功能(增强型型号):

- STC89C52的5-P1.7可用于SPI接口

- STC15系列的P1口可配置为ADC输入

- 典型应用:

- 连接独立按键(需软件消抖)

- 驱动LED指示灯

// 按键扫描示例(P1.0接按键)

if(P1_0 == 0) { // 检测低电平

delay_ms(10); // 消抖

if(P1_0 == 0) {

// 处理按键动作

}

}

P2端口

- 地址总线模式:

- 当访问外部存储器时,输出高8位地址(A8-A15)

- 需配合P0口的低8位地址组成16位地址总线

- 通用I/O特性:

- 输出高电平时由内部上拉电阻提供电流(约50μA)

- 输入前需先置1

- 典型应用:

- 扩展外部存储器时作为高地址线

- 连接数码管的段选信号

// 数码管显示示例 P2 = 0x3F; // 显示数字0(共阴极)

P3端口

P3口的每个引脚均可切换为第二功能:

| 引脚 | 默认功能 | 第二功能 | 寄存器控制 |

| P3.0 | I/O | RXD | SCON.4 (REN=1) |

| P3.1 | I/O | TXD | 自动启用(发送时) |

| P3.2 | I/O | INT0 | TCON.0 (IT0/IE0) |

| P3.3 | I/O | INT1 | TCON.2 (IT1/IE1) |

| P3.4 | I/O | T0 | TMOD.2 (C/T=1) |

| P3.5 | I/O | T1 | TMOD.6 (C/T=1) |

| P3.6 | I/O | WR | 访问外部RAM时自动启用 |

| P3.7 | I/O | RD | 访问外部RAM时自动启用 |

使用注意:

- 启用复用功能时需配置相关寄存器(如TCON、SCON)

- 未使用的第二功能引脚可作为普通I/O

// 串口初始化(使用P3.0/P3.1)

void UART_Init() {

SCON = 0x50; // 模式1,允许接收

TMOD |= 0x20; // 定时器1模式2

TH1 = 0xFD; // 9600bps@11.0592MHz

TR1 = 1;

}

GPIO工作模式与配置

输出模式(控制外部设备)

操作方式:直接写端口寄存器(如 P1 = 0x55;)

代码示例(LED闪烁):

#include <reg52.h>

sbit LED = P1^0; // 定义P1.0控制LED

void delay(unsigned int t) { /* 延时函数 */ }

void main() {

while(1) {

LED = 0; // 低电平点亮LED(共阳接法)

delay(500);

LED = 1; // 高电平熄灭

delay(500);

}

}

输入模式(读取外部信号)

- 关键步骤:

- 向端口写1(使能内部上拉,进入高阻态)

- 读取引脚状态(非锁存器!)

- 代码示例(按键检测):

sbit KEY = P3^2; // 按键接P3.2(INT0引脚)

void main() {

KEY = 1; // 置为输入模式(开启上拉)

while(1) {

if (KEY == 0) { // 按键按下(低电平)

P1 = 0x00; // 所有LED亮

} else {

P1 = 0xFF; // 所有LED灭

}

}

}

GPIO应用陷阱与解决方案

P0口高电平驱动不足

- 问题:P0输出高电平时电压仅2-3V(无法驱动负载)

- 解决:外接7kΩ~10kΩ上拉电阻到VCC

读引脚 vs 读锁存器

错误操作:

if (P1_0 == 1) { ... } // 直接读引脚,可能受外部电路影响

正确做法:

- 输入时:读引脚(如按键检测)

- 输出时:读锁存器(避免“读-修改-写”错误)

P1 |= 0x01; // 读锁存器 → 修改 → 写回(原子操作)

按键抖动干扰

现象:单次按下触发多次中断

解决:

- 硬件:并联1μF电容

- 软件:延时10ms再检测

if (KEY == 0) {

delay_ms(10); // 消抖

if (KEY == 0) { // 确认按下

// 执行操作

while(!KEY); // 等待释放

}

}

GPIO驱动能力计算

51单片机的GPIO驱动能力有限(严格遵循数据手册):

| 参数 | 典型值 | 注意事项 |

| 拉电流(输出1) | 60μA | P0口几乎为0! |

| 灌电流(输出0) | 1.6mA~20mA | 总端口电流<71mA(如P1<8×8.75mA) |

| 输入漏电流 | ±10μA | 悬空时建议启用内部上拉 |

设计原则:

- 驱动LED:优先选择灌电流方式(低电平点亮)

- V驱动大电流设备:必须加三极管/MOS管扩流

高级应用技巧

位操作(sbit关键字)

sbit RELAY = P2^3; // 定义P2.3控制继电器 RELAY = 1; // 开启继电器

总线操作(P0+P2扩展外设)

#define DEV_ADDR 0x8000 // 设备地址(P2.7=1, P2.0~6=0) unsigned char xdata *ptr = DEV_ADDR; // xdata指向外部RAM *ptr = 0x55; // 向设备写入数据(自动激活P0/P2总线功能)

模拟开漏总线(I²C)

sbit SDA = P1^0;

sbit SCL = P1^1;

// SDA输出0

void I2C_SDA_Low() {

SDA = 0; // 强下拉

}

// SDA输出1(释放总线)

void I2C_SDA_High() {

SDA = 1; // 置高(靠外部上拉电阻拉高)

}

总结:GPIO使用黄金法则

- P0作输出必加上拉电阻(除非复用为总线)

- 输入前先写1(使能上拉)

- 严格限制电流(单引脚≤5mA,整端口≤71mA)

- 高频信号走总线(P0/P2优先)

- 复用功能优先用P3(减少硬件设计复杂度)

为什么P0口要开漏输出?

这是一个触及51单片机核心设计智慧的深度问题!P0口采用开漏输出(Open-Drain)结构是英特尔在1980年设计8051时做出的关键决策,背后蕴含多重工程考量。其本质是 「复用引脚功能」与「兼容不同工艺」的经典平衡术。

物理层透视:P0口的内部电路结构

先看简化的P0一位(如P0.0)输出级示意图:

关键特征:

- 缺失「内部固定上拉」:P1/P2/P3口输出级均含固定上拉电阻或MOS管,P0则无。

- 两个MOS管组成推挽变体:

- 下拉MOS(Q1):强驱动能力,导通时拉低引脚至GND。

- 上拉MOS(Q2):仅受总线控制器控制,普通IO模式不开启。

- 核心矛盾:为实现地址/数据总线复用,必须让上拉路径可被精准管理!

根本原因:两大历史性设计目标

目标1:实现地址/数据总线复用(复用引脚)

- 问题: 8051需访问外部存储器时,要求16位地址(A0-A15)+ 8位数据(D0-D7),若独立分配需24引脚!远超当时40pin封装极限。

- 破解方案: 复用引脚!让P0口同时传输低8位地址(A0-A7)和8位数据(D0-D7):

- 先输出地址 → 外部锁存器(如74HC573)在ALE信号下降沿锁存地址

- 再切换传输数据 → 由读写信号控制方向

- 开漏的妙用:当总线控制器激活上拉MOS(Q2)时,形成真正的推挽输出(推电流靠Q2,拉电流靠Q1),此时驱动能力强大到可直接连接存储器和逻辑芯片!若采用传统推挽输出,无法完美实现双向数据总线切换功能。

目标2:兼容NMOS与CMOS工艺(电平适应)

- 历史背景: 初代8051采用NMOS工艺,输出高电平时靠外部上拉提升驱动能力(NMOS自身高电平输出弱)。后虽演进到CMOS工艺,但维持接口兼容性。

- 开漏的兼容性:

- 外接上拉电阻后,可灵活适应 5V TTL电平、3V CMOS电平 甚至更高电压器件(如驱动12V继电器)。

- 作为输入时: 纯悬浮引脚可安全接收外界电压信号(不受内部上拉钳制)。

💡 Intel的工程师洞察:

牺牲P0口普通IO的易用性 → 换取宝贵引脚资源 + 电压兼容弹性

开漏输出 VS 准双向口(P1/P2/P3)关键对比

| 特性 | P0口 (开漏) | P1/P2/P3口 (准双向) |

| 内部上拉方式 | 仅总线模式激活上拉MOS(Q2) | 固定弱上拉电阻(约50KΩ) |

| 普通输出高电平能力 | 无 → 必须外接上拉才能输出’1′ | 有 → 可输出弱高电平(电流≈50uA) |

| 普通输出低电平能力 | 强(电流达1.6mA@5V) | 强(电流≈1.6mA) |

| 作为输入时的状态 | 真·高阻态,外部信号可自由控制高低 | 弱上拉状态,需外部强下拉才能变’0′ |

| 引脚复用功能 | 地址/数据总线复用 | 无复用(P3口部分复用中断/串口等外设功能) |

| 电压兼容性 | 外接上拉后可工作于不同电压系统 | 只能适应本MCU的VCC电平 |

当P0口工作于「地址/数据总线模式」时(即用于访问外部存储器或扩展IO),不需要额外上拉电阻。具体使用场景(无需上拉电阻)

| 应用场景 | 实现方式 | 为什么不需要上拉电阻? |

| 外接外部存储器 | P0作为8位地址总线低字节(A0-A7)+8位数据总线(D0-D7)复用口 | 在总线模式下,当单片机输出高电平时,内部驱动电路会主动导通上拉MOSFET,直接将电平拉至VCC。 |

| 访问扩展并行I/O芯片 | 通过P0口连接如8255、74HC573等并行扩展芯片(使用总线方式通信) | 同上,总线模式激活内部上拉驱动能力。 |

| 硬件译码器输出控制 | P0作为地址线连接译码器(如74HC138)片选信号 | 总线模式下驱动能力足以直接驱动逻辑芯片。 |

关键对比:

- P0口普通IO模式 (LED/按键) → 必须加外部上拉电阻

- P0口总线模式 (外扩RAM/ROM/锁存器) → 不需要外部上拉电阻